首頁故事

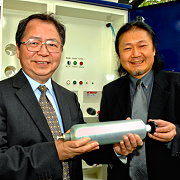

電機系林崇榮教授團隊研發成果將引領下世代最小記憶體【2010.12.27秘書處】

日前,本校電機系林崇榮教授就我國記憶體產業新的技術發展,接受IEEE Spectrum記者專訪。林教授表示他所指導的微電子實驗室,是由數十個研究者所組成的團隊,與工業技術研究院(以下簡稱工研院)的工程師共同合作,花了兩年設計獨一無二的雙極性電晶體,提升了3-D電阻式記憶體單元的可行性。這項成果即將於12月初,在舊金山舉行的IEEE國際電子元件會議中發表。

由清大及工研院共同製作的陣列3-D電阻式記憶體單元,每平方米佔 0.032微米(採用90奈米的互補式金氧半導體邏輯技術),或4倍的平方的最小功能在晶片(4F2專業用語)。林崇榮教授說,高密度三維電阻式記憶體單元的優點包括低電壓操作,更好的可靠性和卓越的可擴展性,他認為這樣一個區域式節能記憶體甚至可能取代快閃記憶體。

林教授指出,形成雙極性電晶體下方的記憶體單元是關鍵。這就像把需要的東西放在地下室的一個單層的房子,而不是擴展鄰近地區。所以不必使用額外的土地。一個雙極性電晶體的選擇也意味著新的電阻式記憶體單元的大小是與互補式金氧半導體(CMOS)邏輯電晶體結構完全不相同的,如柵極長度和氧化層厚度。因此,記憶體單元的佈局可以更容易地安排和縮減到4F2。

關於新的電阻式記憶體單元,林崇榮教授也透露具可節能性。因為雙極性電晶體可以有效地維持每一單位低於2伏特可消除1.5伏特。相反的,最低的外加電壓快閃記憶體單元操作是近10伏特。而在可靠性方面,新的電阻式記憶體可以承受超過1,000萬讀寫/抹除週期且沒有明顯退化,最低可接受的flash為10,000個週期。

林教授的團隊努力做出的新式記憶體,可與製造半導體邏輯晶片的互補式金氧半導體製程相容。正因為如此,記憶體單元可以做得比工程師們的邏輯電路還要來得更小。對於這項電阻最小的非揮發性內儲存式(電阻式記憶體)架構新的發明,目前我國政府認為此技術應特別加強,因為它可能有助於重振國內日漸衰退中的記憶體產業。林教授的研究團隊對台灣的晶圓代工業而言,正是默默的無名的英雄,向人們展示該技術的大規模製造能力。

-

素有「人民總統」之稱的印度前總統,阿布拉•卡藍(Dr. APJ Abdul Kalam),於12月4日蒞臨本校... (繼續閱讀)

-

繼八月初本校針對一、二級主管辦理精實管理研習會後,為了逐步推動並落實校內精實管理,12月13、14... (繼續閱讀)

-

本校99年度「校務發展諮詢委員會議」,12月6日(一),假行政大樓第一會議室舉行,出席委員包括:王... (繼續閱讀)

-

本校校友陳明俊先生,為響應陳力俊校長打造清大為「新能源綠色校園」的治校理念,及慶祝母校建校百... (繼續閱讀)

-

由資工系四年級陳禹琤、馬儀蔓、陳怡君、黃振瑋、薛宇鈞和三年級廖孟楷六位同學組成的團隊,在鍾葉... (繼續閱讀)

-

本校第5屆「傑出產學合作獎」,暨第13屆「新進人員研究獎」頒獎典禮,於11月25日假蘇格拉底二手書... (繼續閱讀)